确保FACE系统的多核分区

介绍

未来机载能力环境(FACE™)联盟每年举办一次技术交流会议和展览。今年的活动原定于9月举行,但因2019冠状病毒病推迟至3月。FACE活动之前,风河系统公司和Rapita系统提供了FACE架构的一些背景,重点是我们的可移植性单元(UoP)“一站式购物”生态系统,以及基于FACE技术标准测试、集成和认证系统的工具。前几篇文章包括:

美国国防部有利于开放架构解决方案,作为快速且以较低的成本更加改进的航空电子硬件。这种解决方案的一个来源是未来的空中能力环境(Face™)联盟,它发布了开放式架构技术标准以及用于在航空电子系统中实施标准的商业模式。面部联盟发布的出版物是公开可用,免费下载。

以前的博客确定了分区和探索在单个核心分区的益处。在这个系列的第四个博客中,我们继续分区的主题,但现在侧重于多核处理器。航空电子系统设计师和集成商设计为面部标准正在采用多核处理器(MCP)以满足未来的性能需求。MCP为航空电子工业提供了一个平台,可以在较低的占地面积中提供更大的性能,转化为具有较低尺寸,重量和功率(交换)的系统。无论这些福利如何,航空电子工业的OEM都会被迫在升级时采用MCP技术,以取代遗产单核设计,因为当今市场上的几乎每个新的处理器都是基于多芯技术。即使在MCP在MCP实施,包括便携性,模块化,减少的集成工作和减少认证工作(由于增量和分区保证),仍然存在仍然保持仍然存在。但是,MCP还在实施和认证方面介绍了额外的复杂性。系统集成商需要有关如何成功的指导。

多核系统保证指南

DO-178C,DO-297和ARINC 653都在单核处理器的背景下写入,因此MCP的引入和使用增加了进一步的复杂性。FAA CAST-32A定位文件解决了MCP保证和最近拟议的咨询通函,该建议与欧盟安全局(EASA)协调。新建议将在美国FAA下的AC 20-193在美国,同一文件将在EASA下的欧洲列为AMC 20-193。

CAST-32A扩展了多核处理器的分区概念,“稳健的时间分区(在MCP上)是在不同核心上托管的分区之间的时间干扰之间的结果时实现的,而不会使软件分区多于其执行时间的分配它在其上执行的核心,而不管是否正在执行其他活动核心或所有其他活动核心都没有执行分区。“

尽管每个美国军队都有自己的适航权威,根据FAA指南的适航证据通常被接受作为认证努力的一部分。具体来说,CAST-32A是美国联邦航空局的指导文件之一,一些军事项目目前正在考虑采用MCP系统。此外,从2019年开始,“计算机系统和软件”第15条的增强工作正在进行中MIL-HDBK-516C适航认证标准。在第15节列出的42项标准中,有20项被确定为需要加强以适应mcp的使用。MIL-HDBK-516C的更新预计在来年。

在多核处理器上运行的脸部符合系统的认证申请人需要满足民用飞行认证指南(例如DO-178C,DO-297和AC 20-193)和/或军用适航指导(例如增强MIL-HDBK-516C的MCP要求)。符合面部技术标准本身并不能确保满足这些标准,尽管面对EA-25小组委员会目前正在进行白皮书,以提供更详细的建议,脸部活动和文物可能有助于标准的航班认证证据如DO-178C和MIL-HDBK-516C。

确保分区,多核系统

当多核处理器首次开始出现在航空电子设备中时,早期采用者通过简单地停用除其中一个核心来避免了一些认证问题。这项工作,因为在许多情况下,单核的性能比旧的UniCore处理器更好。然而,随着年多年来的,各个核心在性能中没有进一步提高,这意味着通过更高处理器计算吞吐量的功能显着提升只能在MCP中的多个核心实现。

即使在单核系统上,证明时间分区的正确性也是一项挑战。虽然在只有一个核心的情况下只能有一个分区运行,但是分区之间仍然可以直接相互干扰,造成不受约束的分区抖动,也就是说,每个分区调度时隙的时间变化没有确定的限制。单核上的分区也可以间接地相互干扰。例如,一个分区可以使用CPU以外的总线主服务器(例如DMA引擎)启动一个操作,它的活动扩展到分区的计划时隙的末端,因此可能与另一个分区的活动重叠或竞争。

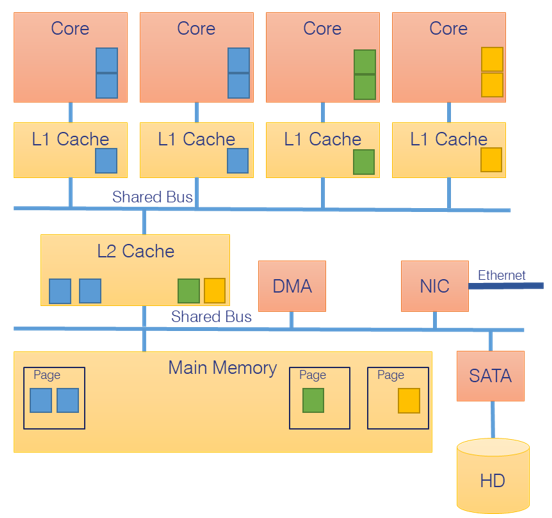

在MCP系统中,多个应用程序现在可以同时运行,每个应用程序在其自己的核心上。有些资源是私有的,独占于单个核心,如L1缓存,如图1中的示例四核架构所示。然而,其他资源是共享的,如L2缓存、主存和I/O设备。因此,不同核上的应用程序可以争夺这些共享资源的访问权,这可能会影响彼此的性能,从而打破分区之间的隔离。

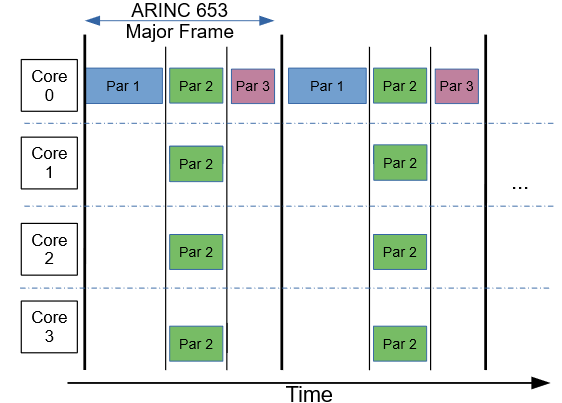

实现时间分区的一种简化方法是在任何给定时间调度单个分区,但允许该分区使用多个核心。这种方法是有限的,因为只有多线程应用程序软件可以利用多个核,而单线程的核在调度的时间窗口内让其他核空闲,如图2所示。

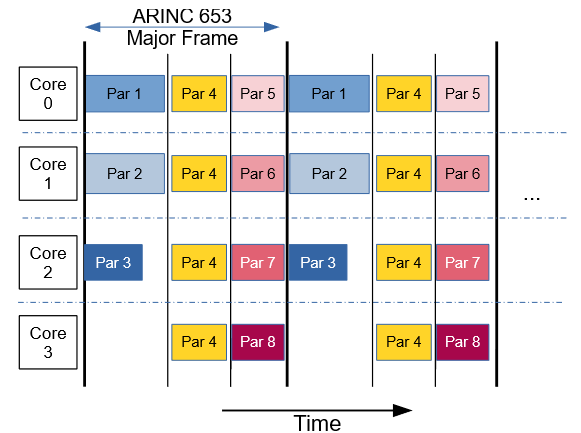

直到最近,mcp的早期采用者才按照DO-297和A(M)C 20-193的指导,尝试使用混合临界软件的所有核。图3说明了这种方法的复杂性,其中多个独立的应用程序可以在同一个分区窗口中运行(每个都在自己的核心上),即使这些应用程序在不同的设计保证级别上经过认证。在这种情况下,具有不同临界性(即不同软件级别)的独立分区能够在相同的调度时间框架内,在不同的内核上同时运行。文中给出了这种复杂方法的一个实例Collins Aerospace已经完成了白皮书中提到的风河项目。

在混合临界多核系统上证明时间分区的正确性是相当具有挑战性的,因为分区可以在不同的核上同时运行。运行在不同内核上的独立分区现在争夺共享资源。这种争用会导致延迟,从而增加软件的最坏情况执行时间(WCET)。当在一个分区中运行的应用程序在没有其他核处于活动状态时可能满足其需求,而在其他核上运行的功能的干扰可能会增加应用程序的WCET,以至于不再满足其需求。由于处理器核心共享访问权限,包括较低级别的高速缓存存储器、主存、I/O设备和总线互连,各种资源可能导致这种干扰。

(m)c 20-193提供了确保多核系统的指导。必须满足十个目标,以证明已经减轻了多核干扰渠道。计划的添加到MIL_HDBK-516C还包括分析干扰通道的标准。干扰通道被定义为计算平台的任何属性“可能导致独立应用之间的干扰”。航空电子系统内的所有干扰通道必须被淘汰,否则它们的冲击必须充分降低,即使在存在与其他核心的最坏情况下的最坏情况水平的情况下,所有应用也满足其时序要求。同样,MIL-HDBK-516C添加要求“执行/控制结构提供的执行率......一致地获得并且足以安全地提供所需的性能。”也就是说,即使在面对多核干扰,必须满足时序要求。成功符合这些标准的目标需要注意在设计早期生命周期期间的干扰渠道的减轻,并在历史后期生命周期阶段仔细注意测量方法。

降低多核干扰

对多核干扰的缓解要求分区彼此隔离。实现分区的多种分离机制可用于系统设计者和集成器,在硬件和/或软件中实现。

一些隔离机制由硬件提供。选择为每个核心专有资源提供的处理器可以消除它们的争用。例如,通常提供至少一级高速缓冲存储器,其是不同的并且对每个核心独一无二的。对于具有强大通往访问的CPU密集型应用程序,私有L1缓存通常足以使软件在很大程度上对来自其他核的干扰非常不敏感。当必须共享资源时,硬件可以通过确保公平访问来提供隔离。即便如此,一个核心的访问可能会影响另一个核心的访问,分解分离。不幸的是,在这样的情况下,硅提供商可能无法提供更好的确定性,因为它会影响原始性能。

尽管硬件可以提供一些隔离机制,但大多数处理器都是为了优化所有核上的平均执行时间而设计的,通常是以牺牲任何一个核上的WCET为代价的。虽然这对于许多商业应用来说是一个很好的权衡,但对于安全关键的航空电子设备来说是一个问题,因为它代表了一种多核干扰的形式。因此,除了通过硬件实现的隔离方法之外,还需要其他隔离方法。

RTOS提供了一些隔离机制。多核RTOS可以管理处理器内核,确保任何一个托管应用程序的使用确定地局限在其分区内,以便所有应用程序满足它们的需求——即使存在多核干扰。这样的RTOS的一个例子是风河VxWorks 653多核版本。

验证多核干扰的缓解

验证多核干扰信道已被减轻是满足A(M)C 20-193目标的关键步骤。由于还没有人证明民用飞机具有混合临界多核系统,所以核查方法才刚刚出现。然而,基于干扰发生器的最佳核查做法正在出现。

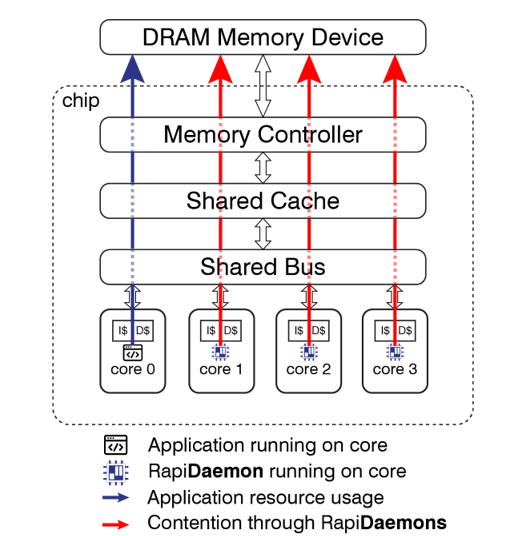

干扰发生器是一种精心设计的软件应用程序,具有较小的代码占用空间,可以创建对目标资源的高带宽使用。例如,Rapita Systems有一个名为RapiDaemons的干扰生成器库,它以共享L3缓存、DDR主存或DMA等资源为目标。这些干扰发生器用于在目标资源上产生核心间压力。例如,图4显示了运行在核心1、2和3上的RapiDaemons和运行在核心0上的应用程序,其中RapiDaemons为访问主内存以及到该资源的逻辑路径上的任何共享资源(包括互连和缓存)创建干扰。

多核干扰综合分析需要识别所有潜在的干扰通道。必须对系统架构进行审核,包括共享资源,包括潜在的模糊或隐藏渠道,其中核心可以追求,例如不公平地仲裁或最后级别缓存,写入端口不足。对于所识别的每个干扰通道,必须设计干扰发生器并校准以应力该通道。对于最高设计保证水平的系统,例如DO-178C级别A和B,必须使用独立性进行此测试。

GAPITA系统对多核定时分析的方法在测试方法中使用两个阶段来测量多核干扰通道。第一阶段是平台表征,其中平台被定义为计算硬件以及RTOS。在这一阶段,我们通过在所有核心上互相竞争互相竞争来检查可能的多核干扰的外界。由于Rapicaemons被调整为强调单个有针对性的共享资源,因此当核心连续竞争该资源时,这提供了可能的性能的签名。即使在应用软件可用之前,也可以进行此阶段。

第二个测试阶段是软件表征。首先在其他核心是休眠状态的同时单独运行,旨在用于飞行的个人软件应用程序,而其他核心是休眠,提供软件时序行为的基线测量。接下来,我们衡量WCET在其他核心运行的Rapidaemon对手存在下增加。通过将WCET与Rapidaemons对手进行比较,我们可以量化最坏情况的多核干扰。此外,可以将具有多核干扰的WCET与系统要求进行比较,以确定它们是否仍然满足 - 从而展示了干扰通道是否已经充分减轻了干扰通道。

集成模块化航空电子设备(IMA)根据DO-297的健壮分区设计,允许增量接受保证证据,在几个独立验证工作的过程中积累认证工件。也就是说,我们可以独立地度量每个分区应用程序,验证多核干扰通道的缓解。任何分区应用程序产生的争用都不会比RapiDaemons产生的争用高。可以为每个分区应用程序单独收集保证证据,即使所有计划的应用程序将在最终系统中集成在一起。此外,当将来添加新软件并将其映射到空闲分区插槽时,不需要重复对现有分区进行计时测试。这种由健壮的分区支持的增量验证方法是减少必须执行的测试数量的一个关键因素。

即使增加了验证的好处,典型多核航空电子系统中干扰信道的复杂性和数量仍然可能导致必须完成的大量测试。因此,工具自动化对于保持验证的进度和成本受到合理约束是很重要的。Rapita Systems的多核时间分析方法使用RapiDaemon干扰发生器和Rapita验证套件软件,将工作流的关键阶段自动化,如图5所示。

然而,并不是所有的事情都可以自动化。来自系统和测试工程师的人类智慧仍然需要在流程开始时识别系统架构中的干扰通道,并在流程结束时正确地解释结果。

总结

系统设计者和集成商需要帮助成功地设计、集成和飞行验证现代多核航空电子系统软件。确保这些系统的安全性,例如实现A(MC)C 20-193(以前的CAST-32A)目标,是具有挑战性的。风河和拉皮塔系统可以成为你成功的向导。Wind River提供操作系统技术,以减少干扰。Rapita提供了一种商业的多核定时分析方法,使用集成在自动化验证工具套件中的RapiDaemon干扰生成器,它可以提供您在项目早期所需的洞察,以及在项目结束时支持a (MC)C 20-193和MIL-HDBK-516C MCP目标所需的工件。

风河系统公司和Rapita系统可以帮助你建立你的脸系统与我们的“一站式购物”的生态系统,从风河OSS和包括工具来测试/集成/认证系统基于面对技术标准,如Rapita系统验证套件和C (MC) 20 - 193 (CAST-32A)合规方案。

在下一篇博客中,我们将概述在追求FACE技术标准的同时,如何将产生的活动和工件用于适航性认证。

关于作者

Alex Wilson是Wind River的航空航天和国防市场部门主任,他负责EMEA,APAC和日本的A&D市场部门。作为Wind River航天和国防行业解决方案团队的一部分,亚历克斯负责商业战略,包括产品要求,销售增长战略和生态系统发展。

Steven H. VanderLeest是Rapita Systems多核解决方案的首席工程师。他曾在IEEE航空和电子系统杂志、IEEE数字航空电子系统会议(DASC)和SAE航空技术杂志上发表过有关航空电子安全的文章。VanderLeest博士也是FACE EA-25适航性委员会的主席。

注:本博客所表达的观点仅为作者个人观点,并不代表FACE联盟的官方立场。